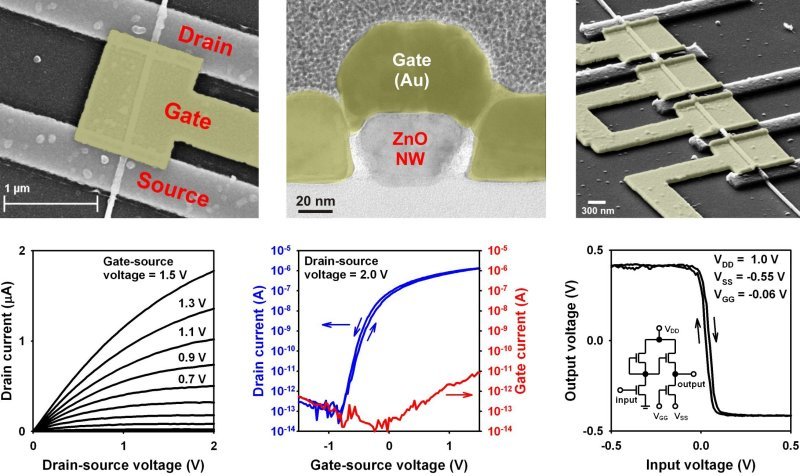

| We have explored the use of inorganic semiconducting nanowires for the realization of high-performance field-effect transistors and logic circuits for electronics applications on flexible plastic substrates. In the first step, high-quality ZnO nanowires were synthesized by a hydrothermal growth method (Lu et al., Chemical Communications, vol. 42, p. 3551, 2006) in an autoclave on commercially available zinc foil and then harvested from the foil by bath sonication. The hydrothermally grown ZnO nanowires have a hexagonal cross-section and a diameter of about 50 nm. High-resolution transmission electron microscopy (HRTEM) indicates that the nanowires are essentially single-crystalline. In the second step, the nanowires were annealed at a temperature of 600 °C in air in order to remove hydrogen dopants unintentionally incorporated into the nanowires during the hydrothermal synthesis; this annealing step reduces the electrical conductivity of the nanowires by several orders of magnitude, thus making them useful as a semiconductor for field-effect transistors. The annealed, semiconducting ZnO nanowires were then dispersed from a liquid suspension onto the intended device substrate, e.g. glass or flexible plastic. Aluminum source and drain contacts and overlapping gold or aluminum gate electrodes were fabricated by electron-beam lithography, plasma cleaning, metal deposition, and lift-off. The gate dielectric is either an alkylphosphonic acid self‑assembled monolayer (SAM) with a thickness of about 2 nm (in the case of gold gate electrodes) or a combination of a SAM and a spontaneously grown aluminum oxide layer with a thickness of a few nanometers (in the case of aluminum gate electrodes). The ZnO-nanowire transistors have on/off current ratios of about 109, a transconductance of up to 50 µS, and maximum switching frequencies of up to 30 MHz. |

|

High-Performance ZnO Nanowire Transistors with Aluminum Top-Gate Electrodes and Naturally Formed Hybrid Self-Assembled Monolayer/AlOx Gate Dielectric

D. Kälblein, H. Ryu, F. Ante, B. Fenk, K. Hahn, K. Kern, H. Klauk

ACS Nano, vol. 8, no. 7, pp. 6840-6848, July 2014

Top-Gate ZnO Nanowire Transistors and Integrated Circuits with Ultrathin Self-Assembled Monolayer Gate Dielectric

D. Kälblein, R. T. Weitz, H. J. Böttcher, F. Ante, U. Zschieschang, K. Kern, H. Klauk

Nano Letters, vol. 11, no. 12, pp. 5309–5315, December 2011

Probing the electrical properties of highly-doped Al:ZnO nanowire ensembles

R. Noriega, J. Rivnay, L. Goris, D. Kälblein, H. Klauk, K. Kern, L. M. Thompson, A. C. Palke, J. F. Stebbins, J. R. Jokisaari, G. Kusinski, A. Salleo

Journal of Applied Physics, vol. 107, no. 7, pp. 074312/1-7, April 2010