## ADVANCED MATERIALS

# **Organic Electronics on Banknotes**

Ute Zschieschang,\* Tatsuya Yamamoto, Kazuo Takimiya, Hirokazu Kuwabara, Masaaki Ikeda, Tsuyoshi Sekitani, Takao Someya, and Hagen Klauk

Modern banknotes include up to 50 different anti-counterfeiting features, such as watermarks, holograms, raised printing, embedded foil strips, fluorescent inks, and many others. To supplement these passive security features, active electronic anti-counterfeiting and tracking features in the form of silicon integrated circuits have been considered,<sup>[1]</sup> but have thus far not been realized, mainly because of the significant thickness of standard silicon wafers (>500 um). The thickness of silicon chips can be reduced to about 20 µm,<sup>[2,3]</sup> but this may still be too thick for incorporation into banknotes. Other techniques allow thin silicon membranes to be transferred from a wafer onto plastic substrates and be processed into flexible circuits.<sup>[4,5]</sup> Although it may be possible to transfer silicon membranes onto banknotes as well, the harsh process conditions during circuit fabrication following the transfer of the membranes may irreversibly damage the banknotes.

In contrast, organic thin-film transistors (TFTs) are readily fabricated on a variety of surfaces, including foils,<sup>[6–10]</sup> fibers,<sup>[11,12]</sup> and paper.<sup>[13–15]</sup> The ability to fabricate organic circuits on banknotes may create the possibility of outfitting banknotes with active electronic security features, provided the device fabrication process does not damage the banknotes and provided the operating voltage and power consumption of the circuits is sufficiently low to allow power being supplied by radio-frequency coupling with low magnetic fields.<sup>[16]</sup>

The key to realizing low-voltage organic TFTs on delicate substrates, such as banknotes, is the use of a high-capacitance gate dielectric prepared under mild thermal and chemical conditions. A promising option are hybrid dielectrics composed of a thin aluminum oxide layer and an alkylphosphonic acid

Dr. U. Zschieschang, Dr. H. Klauk Max Planck Institute for Solid State Research Heisenbergstr. 1, 70569 Stuttgart, Germany E-mail: U.Zschieschang@fkf.mpg.de Dr. T. Yamamoto, Prof. K. Takimiya Department of Applied Chemistry Graduate School of Engineering Institute for Advanced Materials Research Hiroshima University Higashi-Hiroshima, Japan Dr. H. Kuwabara, Dr. M. Ikeda Functional Chemicals R&D Laboratories Nippon Kayaku Co., Ltd., Kita-ku, Tokyo, Japan Prof. T. Sekitani, Prof. T. Someya Department of Electrical Engineering University of Tokyo Tokyo, Japan

### DOI: 10.1002/adma.201003374

COMMUNICATION f f s a i

layer is produced by briefly exposing the surface of the aluminum gate electrodes (bottom-gate structure) to an oxygen plasma, which increases the native AlO<sub>x</sub> thickness to about 3 to 4 nm, depending on the plasma power. The organic monolayer is then allowed to self-assemble on the AlO<sub>x</sub> surface by immersing the substrate in a solution of a commercially available alkylphosphonic acid in a gentle solvent (2-propanol). Anchoring of the alkylphosphonic acid molecules on the AlO<sub>x</sub> surface occurs by heterocondensation of the phosphonic acid groups with surface hydroxyl groups<sup>[20]</sup> and involves the formation of mono-, bi-, or tridentate adsorption complexes (with the phosphonic acid group binding to the surface via one, two, or three P-O-Al linkages).<sup>[21-23]</sup> Mono- or bidentate surface binding would also allow the unreacted phosphonic-acid moieties to crosslink with adjacent molecules. One concern with  $AlO_x/SAM$  dielectrics is whether the  $AlO_x$  surface might be corroded by the alkylphosphonic acid. Corrosion has indeed been observed when using phosphonic acids with very short alkyl chain lengths, such as ethylphosphonic acid,<sup>[19]</sup> but has not been observed with long-chain phosphonic acids, such as octadecylphosphonic acid, which is employed in this work.

self-assembled monolayer (SAM).<sup>[17-19]</sup> The aluminum oxide

$AlO_x/SAM$  gate dielectrics have previously been used to fabricate low-voltage organic complementary circuits on glass<sup>[24]</sup> and on plastic substrates<sup>[25]</sup> and are utilized in this work to realize functional organic TFTs and circuits on banknotes. The transistors and circuits have a thickness of less than 250 nm and can be operated with voltages of about 3 V.

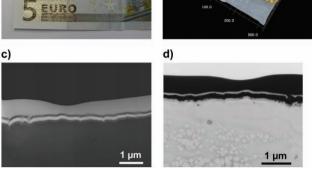

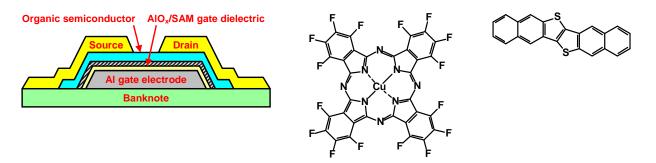

A photograph of a 5-Euro note with arrays of organic TFTs and circuits fabricated directly on the surface of the banknote is shown in Figure 1a. The fabrication process (described in the Supporting Information) is similar to the process previously reported for the fabrication of low-voltage organic TFTs and circuits on glass.<sup>[17]</sup> Except for the formation of the SAM, this is an all-dry manufacturing process that avoids the use of liquids and chemicals. The organic semiconductors, dinaphtho[2,3b:2',3'-f]thieno[3,2-b]thiophene (DNTT)<sup>[26,27]</sup> for the p-channel TFTs and hexadecafluorocopperphthalocyanine (F<sub>16</sub>CuPc)<sup>[28]</sup> for the n-channel TFTs, were both deposited in vacuum. The TFTs employ the inverted staggered (bottom-gate, top-contact) device structure. The metal and semiconductor layers were all patterned using polymer shadow masks.<sup>[24-27]</sup> Mechanical and environmental protection of the TFTs and circuits is in principle possible by covering the devices with a thin organic/ metallic passivation layer deposited at room temperature from the vapor phase.<sup>[29]</sup>

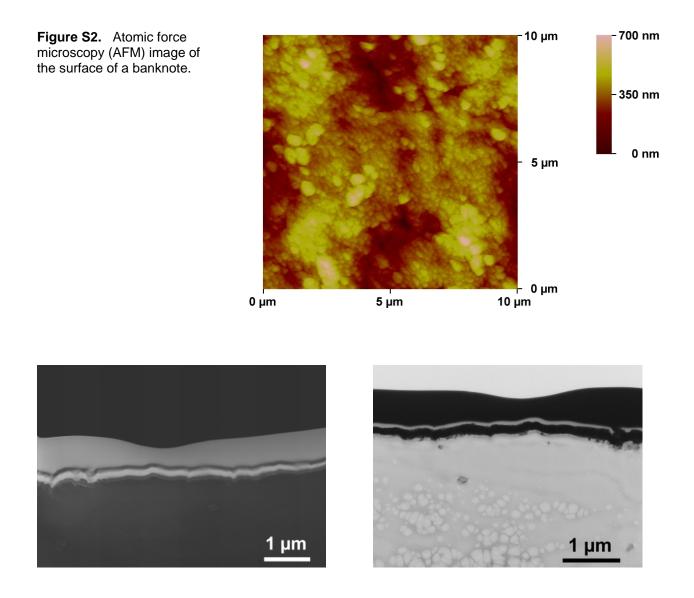

Figure 1 illustrates the significant surface topography of the banknotes. However, because the topography is dominated by long-range waviness, rather than short-range roughness,

**Figure 1.** a) Photograph of a 5-Euro note with arrays of organic transistors and circuits. b) Photograph of an individual transistor on a banknote (image acquired with a Keyence VHX-1000 microscope). c) Crosssectional scanning electron microscopy (SEM) image of the surface of a banknote with an Al/AlO<sub>x</sub>/SAM/Au capacitor. d) Transmission electron microscopy (TEM) image of the surface of a banknote with an Al/AlO<sub>x</sub>/SAM/Au capacitor (image acquired with an HF-3300 Cold-FE TEM, Hitachi High-Technologies Corp.).

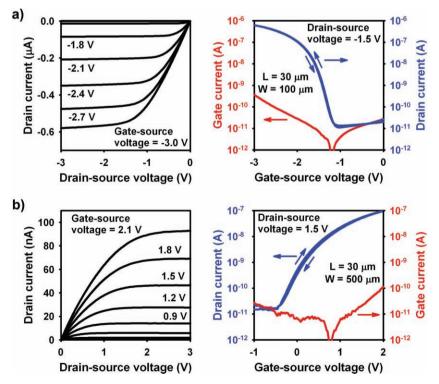

it is possible to obtain organic TFTs with acceptable electrical performance despite this topography. Figure 2 shows the

current-voltage characteristics of a DNTT p-channel TFT and of a F<sub>16</sub>CuPc n-channel TFT on a 5-Euro note. Owing to the small thickness (5.7 nm) and the large capacitance (700 nF cm<sup>-2</sup>) of the AlO<sub>x</sub>/SAM gate dielectric, the TFTs can be operated with low voltages of about 3 V. Despite the small dielectric thickness, the gate leakage current at the maximum gate bias is below 10<sup>-9</sup> A, confirming that the plasma-grown  $AlO_x$ and the solution-processed alkylphosphonic acid SAM form a continuous, conformal coating with useful insulating properties on the aluminum gate electrodes. The fieldeffect mobility extracted from the transfer characteristics of the DNTT p-channel TFT is  $0.2 \text{ cm}^2 \text{ V}^{-1}\text{s}^{-1}$ , which is within a factor of three of the mobility of DNTT TFTs on plastic substrates<sup>[27]</sup> and within an order of magnitude of the mobility on oxidized silicon substrates.<sup>[26]</sup> The subthreshold swing is 110 mV per decade, which is close to that of DNTT TFTs on plastic substrates (100 mV decade<sup>-1</sup>).<sup>[27]</sup> The mobility of the F<sub>16</sub>CuPc n-channel TFTs (0.005 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>) is within a factor of 5 of that of  $F_{16}CuPc$  TFTs on glass.<sup>[17,18,28]</sup>

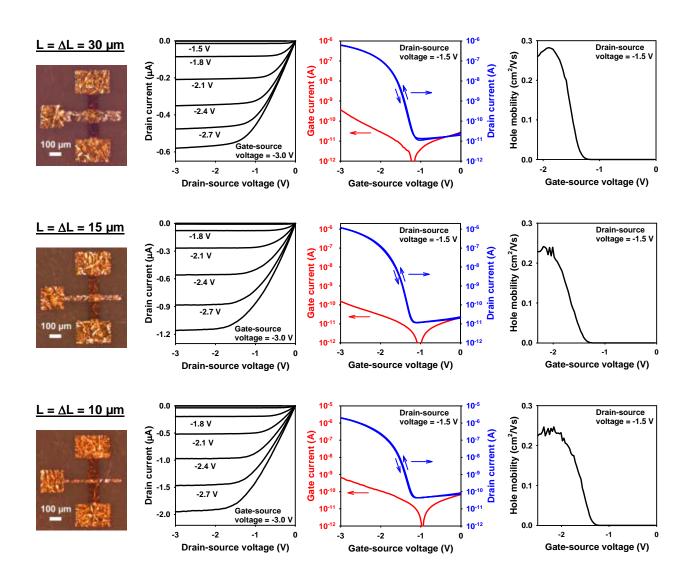

The shortest channel length we are able to realize with polymer shadow masks is 10  $\mu m.$  A comparison of DNTT TFTs with

channel lengths of 10, 15, and 30  $\mu$ m on a 5-Euro note is shown in Figure S4. The mobility of these TFTs is essentially independent of the channel length (0.2 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>). The shorter TFTs have a larger off-state drain current (10<sup>-10</sup> rather than 10<sup>-11</sup> A) and hence a smaller on/off ratio (10<sup>4</sup> rather than 10<sup>5</sup>) than the long-channel devices. For comparison, DNTT TFTs on plastic substrates have off-state drain currents of about 10<sup>-12</sup> A and on/off ratios of about 10<sup>6</sup>.<sup>[22]</sup>

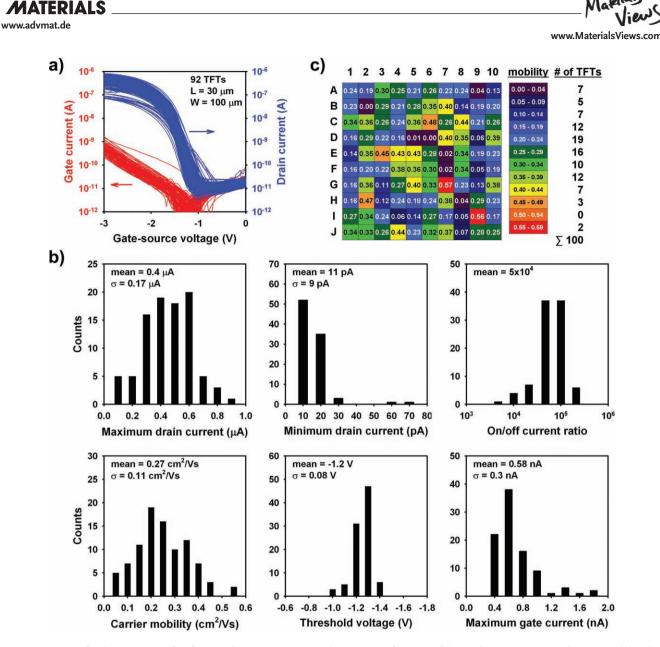

To evaluate the yield and uniformity of organic TFTs on banknotes we measured 100 DNTT transistors with identical channel length (30 µm) and channel width (100 µm) on a 5-Euro note. If we define a TFT as functional if the mobility is at least 0.05  $\rm cm^2~V^{-1}s^{-1}$  and the on/off ratio is at least 3  $\times$ 10<sup>3</sup>, then the yield is 92%. The current-voltage characteristics and the distribution of the electrical parameters of these 92 functional TFTs are shown in Figure 3a and 3b. Compared with organic TFTs on glass substrates, where the yield is essentially 100% and the parameter variations are only a few percent,<sup>[17]</sup> the vield we have obtained on banknotes is substantially lower and the parameter distribution is substantially wider. The threshold voltage, for example, has a standard deviation of 80 mV and varies between -1.0 and -1.4 V (see Figure 3b). Such wide parameter variations would be problematic if the TFTs were employed in active-matrix light-emitting diode displays or in analog or mixed-signal integrated circuits, where image fidelity and circuit linearity are strongly dependent on tight parameter uniformity.<sup>[24]</sup> Properly designed digital circuits, on the other hand, can often tolerate a certain level of parameter variations.[30]

**Figure 2.** a) Current-voltage characteristics of a DNTT p-channel transistor on a 5-Euro note. The field-effect mobility is 0.2 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>. b) Current-voltage characteristics of a F<sub>16</sub>CuPc n-channel transistor on a 5-Euro note. The field-effect mobility is 0.005 cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>.

**Figure 3.** (a) Transfer characteristics of 92 functional DNTT transistors within an array of 100 TFTs fabricated on a 5-Euro note. (b) Statistical distribution of the maximum drain current, the field-effect mobility, the on/off ratio, and the maximum gate current of the 92 functional transistors. (c) Map of the transistor array showing the distribution of the field-effect mobility. The array has an area of  $10 \times 8 \text{ mm}^2$ . Transistors A9, B2, D5, D6, E7, F7 and H8 are considered non-functional because their mobility is below 0.05 cm<sup>2</sup>/Vs, and transistor D4 is non-functional because its on/off ratio is below  $3 \times 10^3$ .

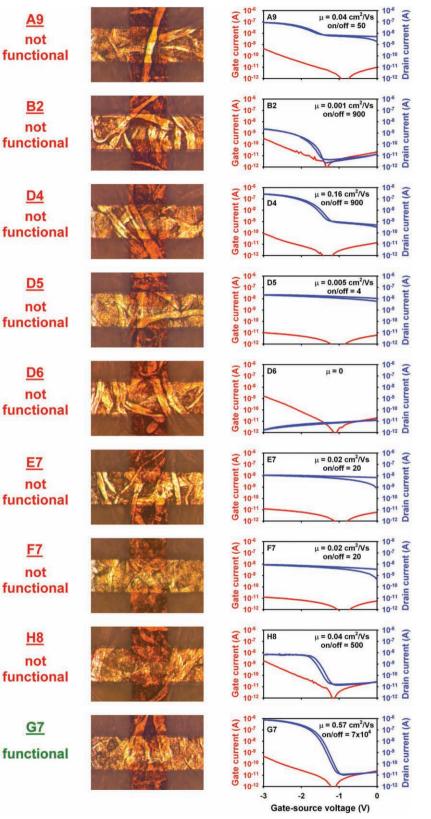

To better understand the mechanisms that limit the device yield on banknotes we have looked for a correlation between the performance of a given TFT within the array and the location of distinct topographical features visible on the surface of the banknote. Figure 3c shows a map of the distribution of the TFT mobility within the array. Transistors A9, B2, D5, D6, E7, F7, and H8 are considered non-functional because their mobility is below 0.05 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and transistor D4 is nonfunctional because it has an on/off ratio of less than  $3 \times 10^3$ . Six of these eight non-functional TFTs (D4, D5, D6, E7, F7, H8) are located in close proximity to each other near the center of the array, which suggests that there might be a common cause for the lack of performance of these devices, possibly related to an agglomeration of fibers at the surface of the banknote in this particular region. **Figure 4** shows a photograph and the current-voltage characteristics of each of the eight nonfunctional TFTs (A9, B2, D4, D5, D6, E7, F7, H8). For comparison, a photograph and the electrical characteristics of transistor G7, which has an excellent mobility (0.57 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) and on/off ratio ( $7 \times 10^4$ ), are also shown. In the photographs of some of the non-functional devices (A9, D4, D5, D6) large fibers that might be deemed responsible for the lack of performance are indeed clearly seen. On the other hand, no large fibers are visible in the photographs of some of the other

Materials

www.MaterialsViews.com

**Figure 4.** Photographs and current-voltage characteristics of eight non-functional transistors (A9, B2, D4, D5, D6, E7, F7, H8) and one functional transistor (G7) out of 100 DNTT transistors on a 5-Euro note. A clear correlation between the presence of large fibers and the transistor performance is not apparent.

ADVANCED MATERIALS

non-functional TFTs (F7, H8). Interestingly, the photograph of the high-performance transistor (G7) clearly shows several large fibers, which apparently have no detrimental effect on the electrical performance of this device. Thus, a clear correlation between surface topography and TFT performance is not immediately apparent.

In order to assess the dynamic performance of organic TFTs on banknotes we fabricated unipolar inverters consisting of two DNTT TFTs (one acting as a drive transistor, the other as a saturated load device; see Figure S6). When operated with a supply voltage of 3 V, these inverters are capable of switching digital signals at frequencies of up to about 2 kHz (see Figure S6). This frequency is several orders of magnitude higher than the operating frequency previously reported for organic TFTs on paper<sup>[13,14]</sup> and is within an order of magnitude of the frequency of low-voltage organic TFTs on plastic substrates.[27]

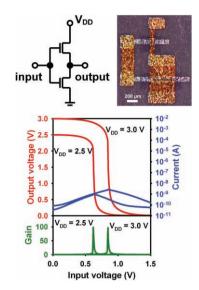

Frequencies of a few kilohertz may already be sufficient for basic logic operations. However, as Figure S6 indicates, the small-signal gain, the output swing, and the noise margins of the unipolar circuits are quite small, which may lead to problems with the signal integrity in circuits of greater complexity.<sup>[30]</sup> Also, unipolar circuits have a relatively large static power consumption, since the load transistor is always conducting. These drawbacks are eliminated in complementary circuits, which employ p-channel and n-channel transistors.<sup>[31]</sup> Figure 5 shows a photograph and the static transfer characteristics of a complementary inverter comprised of a F16CuPc n-channel TFT and a DNTT p-channel TFT on a 5-Euro note. The static characteristics of these complementary inverters (supply voltage about 3 V, static power consumption <1 nW, small-signal gain about 100) are comparable to those of silicon complementary circuits fabricated on silicon membranes and transferred from a silicon wafer onto a flexible plastic substrate.<sup>[4]</sup> The maximum operating frequency of the organic complementary circuits is limited to a few hundred Hertz by the relatively small field-effect mobility of the F16CuPc n-channel TFTs (see Figure S7). However, operating frequencies in the range of a few kilohertz are feasible by employing conjugated organic semiconductors with larger electron mobilities.[32-34]

COMMUNICATION

## ADVANCED MATERIALS

**Figure 5.** Circuit schematic, photograph, and static transfer characteristics of an organic complementary inverter on a 5-Euro note.

### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

### Acknowledgements

The authors thank Benjamin Stuhlhofer at the Max Planck Institute for Solid-State Research for expert technical assistance and Richard Rook at CADiLAC Laser for providing high-quality polymer shadow masks. We gratefully acknowledge the financial support provided by the New Energy and Industrial Technology Development Organization (NEDO) of Japan.

> Received: September 16, 2010 Revised: November 1, 2010

Published online: December 6, 2010

- J. Yoshida, Integrating Touch Interfaces, *EE Times*, 19 December 2001 (available at http://www.eetimes.com/story/OEG20011219S0016).

- [2] M. Zimmermann, J. N. Burghartz, W. Appel, N. Remmers, C. A. Burwick, *IEEE International Electron Devices Meeting Technical Digest* 2006, 1010.

- [3] H. Rempp, J. Burghartz, C. Harendt, N. Pricopi, M. Pritschow, C. Reuter, H. Richter, I. Schindler, M. Zimmermann, *IEEE International Solid State Circuits Conference Technical Digest* **2008**, 334.

- [4] D. H. Kim, J.-H. Ahn, W. M. Choi, H.-S. Kim, T.-H. Kim, J. Song, Y. Y. Huang, Z. Liu, C. Lu, J. A. Rogers, *Science* **2008**, *320*, 507.

- [5] H. C. Yuan, G. K. Celler, Z. Ma, J. Appl. Phys. 2007, 102, 034501.

- [6] J. A. Rogers, Z. Bao, K. Baldwin, A. Dodabalapur, B. Crone, V. R. Raju, V. Kuck, H. Katz, K. Amundson, J. Ewing, P. Drzaic, Proc. Natl. Acad. Sci. USA 2001, 98, 4835.

www.MaterialsViews.com

- [7] G. H. Gelinck, H. E. A. Huitema, E. van Veenendaal, E. Cantatore, L. Schrijnemakers, J. B. P. H. Van Der Putten, T. C. T. Geuns, M. Beenhakkers, J. B. Giesbers, B. H. Huisman, E. J. Meijer, E. M. Benito, F. J. Touwslager, A. W. Marsman, B. J. E. van Rens, D. M. de Leeuw, *Nat. Mater.* 2004, *3*, 106.

- [8] L. Zhou, A. Wanga, S. C. Wu, J. Sun, S. Park, T. N. Jackson, Appl. Phys. Lett. 2006, 88, 083502.

- [9] T. Sekitani, M. Takamiya, Y. Noguchi, S. Nakano, Y. Kato, T. Sakurai, T. Someya, *Nat. Mater.* 2007, 6, 413.

- [10] C. J. Bettinger, Z. Bao, Adv. Mater. 2010, 22, 651.

- [11] J. Granstrom, H. E. Katz, J. Mater. Res. 2004, 19, 3540.

- [12] J. Lee, V. Subramanian, IEEE Trans. Electron Devices 2005, 52, 269.

- [13] P. Andersson, D. Nilsson, P. O. Svensson, M. Chen, A. Malmström, T. Remonen, T. Kugler, M. Berggren, Adv. Mater. 2002, 14, 1460.

- [14] F. Eder, H. Klauk, M. Halik, U. Zschieschang, G. Schmid, C. Dehm, *Appl. Phys. Lett.* **2004**, *84*, 2673.

- [15] Y. H. Kim, D. G. Moon, J. I. Han, *IEEE Electron Device Lett.* 2004, 25, 702.

- [16] K. Myny, S. Steudel, S. Smout, P. Vicca, F. Furthner, B. Van Der Putten, A. K. Tripathi, G. H. Gelinck, J. Genoe, W. Dehaene, P. Heremans, Org. Electron. 2010, 11, 1176.

- [17] H. Klauk, U. Zschieschang, J. Pflaum, M. Halik, Nature 2007, 445, 745.

- [18] U. Zschieschang, M. Halik, H. Klauk, Langmuir 2008, 24, 1665.

- [19] A. Jedaa, M. Burkhardt, U. Zschieschang, H. Klauk, D. Habich, G. Schmid, M. Halik, Org. Electronics 2009, 10, 1442.

- [20] H. Y. Nie, Anal. Chem. 2010, 82, 3371.

- [21] P. H. Mutin, G. Guerrero, A. Vioux, J. Mater. Chem. 2005, 15, 3761.

- [22] M. J. Pellerite, T. D. Dunbar, L. D. Boardman, E. J. Wood, J. Phys. Chem. B 2003, 107, 11726.

- [23] R. Luschtinetz, A. F. Oliveira, H. A. Duarte, G. Seifer, Z. Anorg. Allg. Chem. 2010, 636, 1506

- [24] W. Xiong, Y. Guo, U. Zschieschang, H. Klauk, B. Murmann, IEEE J. Solid-State Circuits 2010, 45, 1380.

- [25] K. Ishida, N. Masunaga, Z. Zhou, T. Yasufuku, T. Sekitani, U. Zschieschang, H. Klauk, M. Takimiya, T. Someya, T. Sakurai, *IEEE J. Solid-State Circuits* **2010**, *45*, 249.

- [26] T. Yamamoto, K. Takimiya, J. Am. Chem. Soc. 2007, 129, 2224.

- [27] U. Zschieschang, F. Ante, T. Yamamoto, K. Takimiya, H. Kuwabara, M. Ikeda, T. Sekitani, T. Someya, K. Kern, H. Klauk, *Adv. Mater.* 2010, 22, 982.

- [28] M. M. Ling, Z. Bao, Org. Electron. 2006, 7, 568.

- [29] T. Sekitani, H. Nakajima, H. Maeda, T. Fukushima, T. Aida, K. Hata, T. Someya, Nat. Mater. 2009, 8, 494.

- [30] D. Bode C. Rolin, S. Schols, M. Debucquoy, S. Steudel, G. H. Gelinck, J. Genoe, P. Heremans, *IEEE Trans. Electron Devices* 2010, *57*, 201.

- [31] B. K. Crone, A. Dodabalapur, R. Sarpeshkar, R. W. Filas, Y. Y. Lin, Z. Bao, J. H. O'Neill, W. Li, H. E. Katz, J. Appl. Phys. 2001, 89, 5125.

- [32] H. Yan, Z. Chen, Y. Zheng, C. Newman, J. R. Quinn, F. Dötz, M. Kastler, A. Facchetti, *Nature* **2009**, 457, 679.

- [33] R. Schmidt, J. H. Oh, Y. S. Sun, M. Deppisch, A. M. Krause, K. Radacki, H. Braunschweig, M. Könemann, P. Erk, Z. Bao, F. Würthner, J. Am. Chem. Soc. 2009, 131, 6215.

- [34] J. H. Oh, S. L. Suraru, W. Y. Lee, M. Könemann, H. W. Höffken, C. Röger, R. Schmidt, Y. Chung, W. C. Chen, F. Würthner, Z. Bao, *Adv. Funct. Mater.* 2010, 20, 2148.

## **Organic Electronics on Banknotes**

By Ute Zschieschang, Tatsuya Yamamoto, Kazuo Takimiya, Hirokazu Kuwabara, Masaaki Ikeda, Tsuyoshi Sekitani, Takao Someya, and Hagen Klauk

### **1. Device Fabrication Process**

The organic TFTs employ the inverted staggered (bottom-gate, top-contact) device structure and are fabricated directly on the surface of the banknotes (see Figure S1).

In the first step of the device process, the gate electrodes of the TFTs are defined by evaporating 70 nm thick aluminum through a polymer shadow mask (CADiLAC Laser, Hilpoltstein, Germany).

To create access to the gate electrodes, 50 nm thick gold is then evaporated through a second shadow mask in specific areas on the aluminum.

To form the gate dielectric, the banknote is then exposed to an oxygen plasma for a few seconds (plasma power: 150 W, duration: 15 s; increases the thickness of the native  $AlO_x$  layer from ~1.5 to 3.6 nm) and then immersed in a 2-propanol solution of *n*-octadecylphosphonic acid (from PCI Synthesis) for about one hour (results in a 2.1 nm thick SAM on the AlO<sub>x</sub> surface).

50 nm of hexadecafluorocopperphthalocyanine ( $F_{16}$ CuPc; from Sigma Aldrich) and dinaphtho[2,3b:2',3'-f]thieno[3,2-b]thiophene (DNTT) are then deposited in vacuum through a third and fourth shadow mask as the organic semiconductors for the n-channel and p-channel TFTs. During the semiconductor depositions the banknote is held at temperatures of 90 °C for the  $F_{16}$ CuPc and 60 °C for the DNTT deposition, since this was found to give the best device performance.

TFTs and circuits are completed by evaporating 100 nm thick gold through a fifth shadow mask to define the source and drain contacts.

Except for the formation of the phosphonic acid SAM, this is an all-dry manufacturing process. The highest process temperature is 90 °C. During the depositions, the banknote is always covered by a shadow mask, so the materials are deposited only where needed for the devices, and no processing is required to pattern the films or remove excess material. The formation of the AlO<sub>x</sub> is specific to the aluminum surfaces, and the formation of the SAM is specific to the plasma-generated  $AlO_x$ surfaces, so these two materials also do not require post-growth patterning. Neither the oxygen-plasma exposure to form the thin  $AlO_x$  layer, nor the exposure to 2-propanol for the formation of the self-assembled monolayer, nor heating to 90 °C during the semiconductor deposition cause any detectable damage to the banknotes.

**Figure S1.** <u>Left:</u> Schematic cross-section of the organic thin-film transistors (TFTs). <u>Center:</u> Hexadecafluorocopperphthalocyanine (F<sub>16</sub>CuPc), the semiconductor for the n-channel TFTs. <u>Right:</u> Dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT), the semiconductor for the p-channel TFTs.

### **2. Electrical Characterization**

All of the electrical measurements are performed in ambient air at room temperature under weak yellow laboratory light.

### **<u>3. Microscopy Images</u>**

Figure S2 and Figure S3 show atomic force microscopy (AFM), cross-sectional scanning electron microscopy (SEM), and cross-sectional transmission electron microscopy (TEM) images of the surface of a banknote (The latter two are also shown in Figure 1 and are reproduced here for better clarity.)

**Figure S3.** Cross-sectional scanning electron microscopy (SEM; left) and transmission electron microscopy (TEM; right) images of the surface of a banknote with an Al/AlO<sub>x</sub>/SAM/Au capacitor.

#### **4. Lateral Transistor Dimensions**

The maximum frequency  $f_T$  at which a field-effect transistor can be operated is determined by its transconductance  $g_m$  and gate capacitance  $C_{gate}$ :

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi C_{\rm gate}}$$

where

$$g_{m} = \frac{\partial I_{D}}{\partial V_{GS}} = \frac{\mu C_{diel} W V_{DS}}{L}$$

and

$$C_{gate} \approx C_{diel} W(L + \Delta L)$$

so that

$$f_{\rm T} = \frac{\mu V_{\rm DS}}{2\pi L (L + \Delta L)} \tag{1}$$

where  $I_D$  is the drain current,  $V_{GS}$  and  $V_{DS}$  are the gate-source and drain-source voltage,  $\mu$  is the carrier mobility, W is the channel width, and  $C_{diel}$  is the gate dielectric capacitance per unit area (here:  $C_{diel} = 700 \text{ nF/cm}^2$ ).

It can be seen that transistor operation at high frequencies requires a small channel length (L) and gate-to-contact overlap ( $\Delta$ L). Figure S4 shows photographs and electrical characteristics of DNTT transistors on a 5-Euro note with channel length and gate to source overlap ranging from 30 µm to 10 µm. All TFTs were patterned using manually aligned polymer shadow masks.

According to Equation (1), TFTs with channel length and gate overlap of 10  $\mu$ m has a maximum frequency f<sub>T</sub> of about 10 kHz.

**Figure S4.** Current-voltage characteristics of DNTT TFTs with a channel length and a gate-to-contact overlap of 30  $\mu$ m, 15  $\mu$ m and 10  $\mu$ m on a 5-Euro note. All three TFTs have a channel width of 100  $\mu$ m. The carrier field-effect mobility is between 0.2 and 0.3 cm<sup>2</sup>/Vs for all three TFTs.

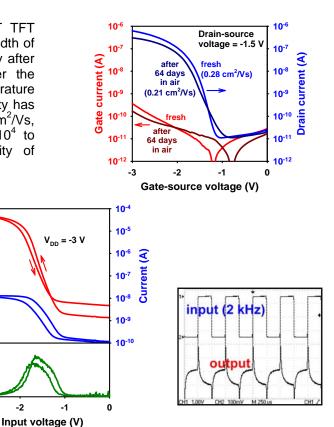

Figure S5. Transfer characteristics of a DNTT TFT with a channel length of 30 µm and a channel width of 100 µm on a 5-Euro note measured immediately after fabrication ("fresh") and measured again after the banknote had been exposed to air at room temperature for 64 days. As can bee seen, the carrier mobility has decreased only slightly, from 0.28 to 0.21 cm<sup>2</sup>/Vs, while the on/off ratio has decreased from 5×10<sup>4</sup> to 3×10<sup>4</sup>. This confirms the excellent air-stability of dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene.

V<sub>DD</sub>

TFT

TFT

O

input

p-channel

ooutput

p-channel

Figure S6. Circuit schematic, photograph, static voltage transfer characteristics, and dynamic switching characteristics of an organic unipolar inverter based on DNTT p-channel TFTs on a 5-Euro note. The inverter shows the correct logic function and responds to input signals with a frequency of a few kilohertz.

-2

0.0

Output voltage (V) -1.0 -1.5

-2.0

2 2 Cain

0 -3

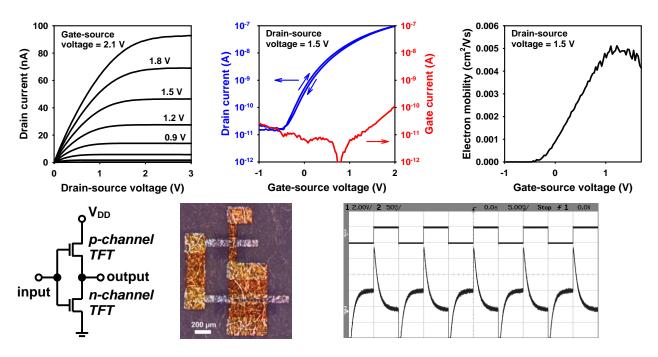

Figure S7. Top: Current-voltage characteristics of an F<sub>16</sub>CuPc n-channel TFT on a 5-Euro note. Bottom: Circuit schematic, microscope photograph, and dynamic switching characteristics of a complementary inverter based on organic p-channel and n-channel TFTs on a 5-Euro note. The inverter shows the correct logic function (see Figure 5) and responds to input signals with a frequency of a few hundred Hertz.

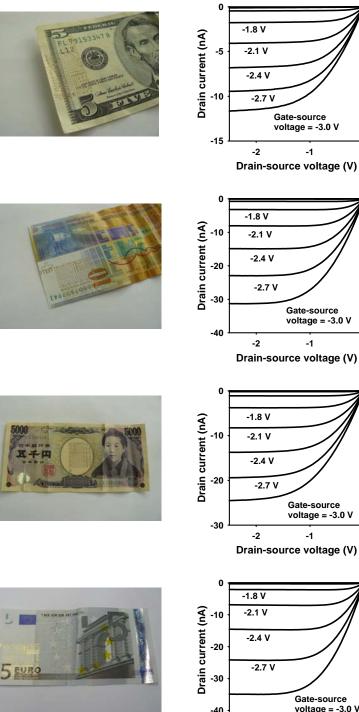

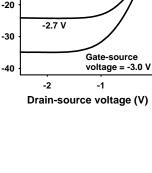

Figure S8. Organic TFTs have also been fabricated on US-dollar, Swiss-franc and Japanese-yen notes. This figure shows the electrical characteristics of p-channel TFTs with a channel length of 30 µm and a channel width of 100 µm using pentacene as the semiconductor. The carrier mobility of these TFTs is between 0.01 and  $0.02 \text{ cm}^2/\text{Vs}$ , and the on/off ratio is between  $10^3$  and 10<sup>4</sup>.

-1

Gate-source voltage = -3.0 V

-1

Gate-source voltage = -3.0 V

-1

-1

0

0

0

0