## High-Performance ZnO Nanowire Transistors with Aluminum Top-Gate Electrodes and Naturally Formed Hybrid Self-Assembled Monolayer/AlO<sub>x</sub> Gate Dielectric

Daniel Kälblein,<sup>†</sup> Hyeyeon Ryu,<sup>†</sup> Frederik Ante,<sup>†</sup> Bernhard Fenk,<sup>†</sup> Kersten Hahn,<sup>‡</sup> Klaus Kern,<sup>†,§</sup> and Hagen Klauk<sup>†,\*</sup>

<sup>†</sup>Max Planck Institute for Solid State Research, 70569 Stuttgart, Germany, <sup>‡</sup>Max Planck Institute for Intelligent Systems, 70569 Stuttgart, Germany, and <sup>§</sup>Institut de Physique de la Matière Condensée, École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland

**ABSTRACT** A method for the formation of a low-temperature hybrid gate dielectric for highperformance, top-gate ZnO nanowire transistors is reported. The hybrid gate dielectric consists of a selfassembled monolayer (SAM) and an aluminum oxide layer. The thin aluminum oxide layer forms naturally and spontaneously when the aluminum gate electrode is deposited by thermal evaporation onto the SAM-covered ZnO nanowire, and its formation is facilitated by the poor surface wetting of the aluminum on the hydrophobic SAM. The hybrid gate dielectric shows excellent electrical insulation and can sustain voltages up to 6 V. ZnO nanowire transistors utilizing the hybrid gate dielectric feature a large transconductance of 50  $\mu$ S and large on-state currents of up to 200  $\mu$ A at gate-source voltages of 3 V. The large on-state current is sufficient to drive organic light-emitting diodes with an active area of 6.7 mm<sup>2</sup> to a brightness of 445 cd/m<sup>2</sup>. Inverters based on ZnO nanowire transistors and thin-film carbon load resistors operate with frequencies up to 30 MHz.

KEYWORDS: zinc oxide · nanowire transistors · hybrid dielectric · organic light-emitting diodes

eield-effect transistors (FETs) based  $\blacksquare$  on individual<sup>1-4</sup> or thin films<sup>5-7</sup> of semiconducting nanowires are potentially useful for high-performance electronics on flexible polymeric substrates.<sup>8</sup> One promising target application is to replace thin-film transistors (TFTs) in active-matrix organic light-emitting diode (AMOLED) displays.9-11 Compared to TFTs based on hydrogenated amorphous silicon or organic semiconductors, single-crystal-nanowire FETs provide larger charge-carrier mobilities and therefore permit faster pixel charging. Further, the smaller footprint of nanowire FETs compared to TFTs potentially provides a larger aperture ratio since a larger portion of the pixel area is available for the organic LED. In order to benefit from high-performance FETs based on semiconducting nanowires on flexible plastic substrates, it is important that the temperature during the FET fabrication

process is below ~150 °C. Although the synthesis of single-crystalline semiconductor nanowires often involves high temperatures ( $T \gg 150$  °C) that are not compatible with plastic substrates, it is in general possible to transfer the nanowires from a temperature-compatible sacrificial growth substrate to the low-temperature target substrate.<sup>8</sup>

To fabricate the gate dielectric, lowtemperature atomic layer deposition (ALD) is often utilized.<sup>12,13</sup> This process allows the fabrication of thin dielectric layers that provide excellent electrical insulation and a large capacitance per unit area<sup>14–16</sup> at low process temperatures (~150 °C). However, while ALD offers precise control of the dielectric film thickness, control in the lateral dimension is more difficult. Standard lithographic patterning techniques, such as electron-beam lithography, are usually not applicable because the ALD films also

\* Address correspondence to h.klauk@fkf.mpg.de.

Received for review March 17, 2014 and accepted June 18, 2014.

Published online June 18, 2014 10.1021/nn501484e

© 2014 American Chemical Society

VOL. 8 • NO. 7 • 6840-6848 • 2014

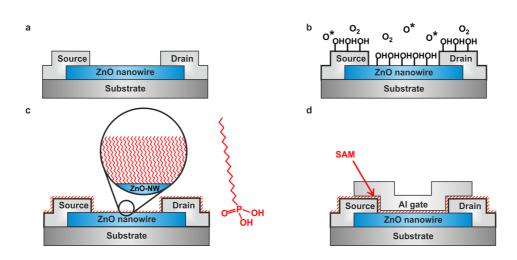

Figure 1. Fabrication of top-gate ZnO nanowire transistors. (a) Source and drain contacts are patterned on randomly dispersed ZnO nanowires by electron-beam lithography and thermal evaporation of 80 nm thick aluminum. Immediately prior to the aluminum evaporation, the contact regions are exposed to an argon-plasma treatment to increase the conductivity of the ZnO nanowire below the contacts. (b) ZnO nanowire and the aluminum contacts are exposed to a soft oxygen plasma ( $30 \text{ sccm O}_2$ , 10 mTorr, 50 W, 20 s) to clean the surfaces and increase the density of hydroxyl groups. (c) Sample is immersed into a solution of 2-propanol containing 1 mmol of octadecylphosphonic acid. The self-assembled monolayer readily forms on the surfaces of the aluminum contacts and the ZnO nanowire. (d) Top-gate electrode is patterned by electron-beam lithography and thermal evaporation of 80 nm thick aluminum.

nucleate on the side walls of the resist masks, making the lift-off process difficult. Therefore, an additional patterning step and a subtractive process are usually required to control the lateral dimensions of ALD films. Here we demonstrate an alternative approach for the formation of a high-quality, high-capacitance gate dielectric in a top-gate FET configuration that can be fabricated at a low temperature (100 °C) to be fully compatible with flexible plastic substrates and without the need for subtractive dielectric patterning. In a previous report, we demonstrated the fabrication of low-voltage ZnO nanowire transistors and circuits with a very thin gate dielectric consisting of an organic selfassembled monolaver (SAM) and patterned gold topgate electrodes.<sup>17</sup> While these transistors showed excellent static and dynamic performance, a significant increase of the gate current was observed when the gate-source voltage was increased above 0.5 V, making it difficult to integrate these transistors with organic LEDs for active-matrix displays.

Here we show that by replacing the gold top-gate electrode with aluminum, the thickness of the gate dielectric increases by a few nanometers due to the spontaneous formation of an interfacial aluminum oxide (AlO<sub>x</sub>) layer at the interface between the SAM-covered ZnO nanowire and the aluminum top-gate electrode. This hybrid organic/inorganic (SAM/AlO<sub>x</sub>) gate dielectric shows significantly improved insulation compared to the SAM-only dielectric in our previous study.<sup>17</sup> This makes it possible to apply larger voltages to the transistors and hence to accumulate a larger density of charge carriers in the channel and to obtain a larger transconductance and a larger cutoff frequency while maintaining low gate currents of about 1 pA. Since the aluminum oxide forms naturally during the

deposition of the aluminum top-gate electrode, no additional patterning step to remove the gate dielectric layer in undesired locations is required. We demonstrate that the aluminum top-gate FETs are fully compatible with organic LEDs and operate at frequencies up to 30 MHz.

#### **RESULTS AND DISCUSSION**

The ZnO nanowires are synthesized by a wetchemical approach utilizing a metallic zinc foil as the growth substrate.<sup>18</sup> The as-grown nanowires have a large charge-carrier density in the range of  $10^{19}$  cm<sup>-3</sup>, due to dopants that are unintentionally incorporated during the nanowire synthesis. Transistors based on asgrown nanowires have field-effect mobilities in the range of 20–40 cm<sup>2</sup>/Vs, but the large charge-carrier concentration makes it difficult to modulate the drain current with the gate-source voltage. In order to reduce the charge-carrier density, a thermal anneal at 600 °C for 15 min in air is required, as described in our previous study.<sup>17</sup> The field-effect mobility of transistors based on wet-chemically synthesized and post-growth-annealed ZnO nanowires in a global back-gate geometry is usually around 50 cm<sup>2</sup>/Vs.

Figure 1 shows the fabrication process for the topgate ZnO nanowire transistors. The ZnO nanowires are randomly dispersed on the device substrate (heavily doped silicon with 100 nm thick thermally grown SiO<sub>2</sub> or glass) and located by microscopy with respect to predefined unique alignment markers. Next, the source and drain contacts are patterned using electronbeam lithography (EBL), vacuum evaporation of 80 nm thick aluminum, and lift-off (Figure 1a). Immediately prior to the evaporation of the aluminum source and drain contacts, the contact regions of the nanowires

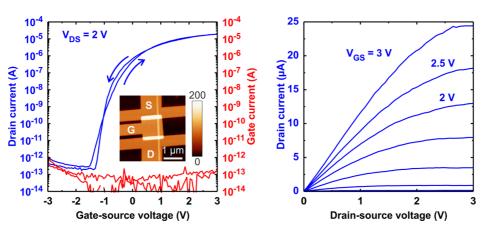

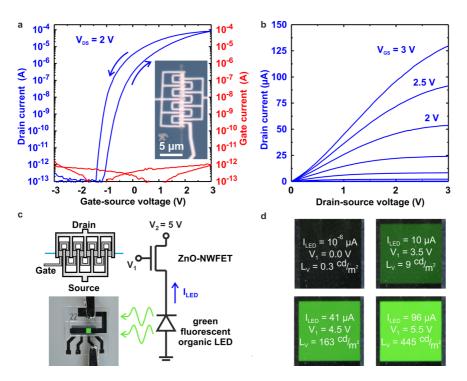

Figure 2. Transfer and output characteristics of a ZnO nanowire transistor with an aluminum top-gate electrode. The inset shows an AFM image (*z*-scale: 0–200 nm) of the transistor, based on a nanowire with a thickness of 35 nm and having a channel length of 1  $\mu$ m. The transistor has a transconductance of 7  $\mu$ S, an on/off ratio 10<sup>7</sup>, and a subthreshold slope of 150 mV/dec. The gate current is below 1 pA for –3 V <  $V_{GS}$  < 3 V.

are briefly exposed to an argon plasma (30 sccm Ar, 10 mTorr, 100 W, 15 s). This argon-plasma treatment cleans the surface of the nanowires and is known to increase the surface conductivity of the ZnO nanowires due to preferential sputtering of oxygen from the ZnO lattice.<sup>19,20</sup> During this argon-plasma treatment, the channel region of the nanowires is protected by electron-beam resist (poly(methyl methacrylate), PMMA). In the next step, the sample is again spin-coated with PMMA, and the regions for the gate electrodes are defined by EBL. After the resist is developed, the substrate is exposed to a soft oxygen plasma (30 sccm  $O_{2}$ , 10 mTorr, 50 W, 20 s). The purpose of the oxygenplasma treatment is to increase the density of hydroxyl groups on the surface of the ZnO nanowire channel and on the surface of the aluminum source and drain contacts in the area of the gate electrode (Figure 1b). Immediately after the oxygen-plasma treatment, the sample is immersed into a solution of octadecylphosphonic acid molecules in 2-propanol, which leads to the formation of a self-assembled monolayer on the ZnO nanowire and on the aluminum contacts (Figure 1c). After 1 h, the substrate is removed from the solution, rinsed with 2-propanol, and baked on a hot plate at 100 °C for 10 min to evaporate excess solvent and improve the quality of the SAM. Finally, 80 nm thick aluminum is deposited by thermal evaporation to form the metal gate electrode, followed by the lift-off of excess metal (Figure 1d).

Figure 2 shows the transfer and output characteristics of a ZnO nanowire transistor with an aluminum top-gate electrode and a channel length of 1  $\mu$ m. The thickness of the nanowire measured by atomic force microscopy (AFM) is 35 nm (see inset in Figure 2). The transistor has an on/off current ratio of 10<sup>7</sup>, a subthreshold slope of 150 mV/dec, and a peak transconductance of 7  $\mu$ S. The gate current of the transistor is no greater than ~0.1 pA over the entire gate-source voltage range.

In our previous study, we investigated the insulating properties of SAMs of alkylphosphonic acid molecules

in ZnO nanowire transistors with top-gate electrodes made of gold instead of aluminum.<sup>17</sup> This study showed that the SAM gate dielectric effectively reduces the gate current of gold top-gate ZnO nanowire transistors by 3 orders of magnitude compared to gold top-gate ZnO nanowire MESFETs where the SAM gate dielectric was omitted. However, the gate current of the gold top-gate transistors with SAM gate dielectric still increased considerably for positive gate-source voltages exceeding 0.5 V, which means that these FETs cannot be integrated with organic LEDs for displays since organic LEDs typically require voltages of about 3 V.<sup>21</sup> The observed increase in gate current for positive voltages was attributed to the diminishing height of the Schottky barrier that forms between the gold gate electrode and the ZnO nanowire. Based on these observations for ZnO nanowire transistors with gold top-gate electrodes, an even larger gate current for positive voltages would be expected when the gold is substituted by aluminum because the work function difference between aluminum and ZnO ( $\Phi_{ZnO-Al} < 0.1 \text{ eV}$ ) is even smaller compared to that between gold and ZnO ( $\Phi_{ZnO-Au} \sim 0.65$  eV).<sup>22,23</sup> However, as can be seen from Figure 2, ZnO nanowire transistors that employ an aluminum top-gate electrode withstand much higher voltages up to  $V_{GS} = 3$  V without showing a significant increase of the gate current.

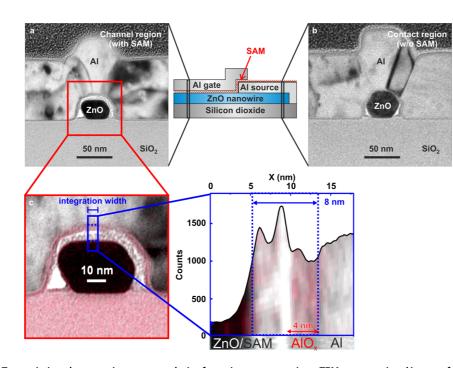

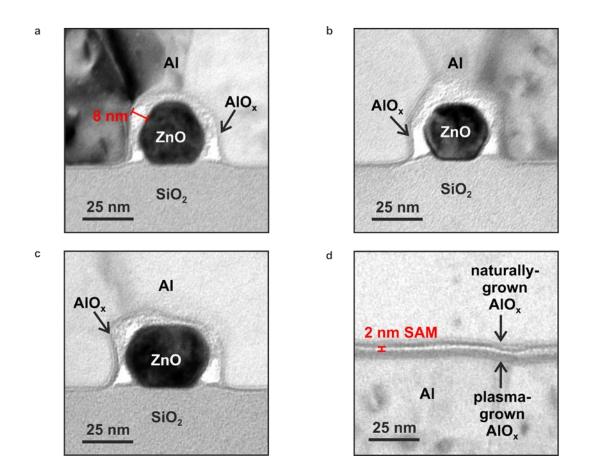

In order to investigate the composition of the gate dielectric of aluminum top-gate ZnO nanowire transistors, the transistor cross section has been investigated by transmission electron microscopy (TEM). With the help of a focused ion beam, nominally 50 nm thick slices of the transistor cross section have been cut out and transferred to the TEM. Figure 3a shows the TEM image of the nanowire cross section cut out from the channel region of the transistor. In this region, the nanowire was covered with an octadecylphosphonic acid SAM prior to the deposition of the aluminum gate electrode. For comparison, Figure 3b shows the cross

IAI

www.acsnano.org

Figure 3. Transmission electron microscopy analysis of transistor cross sections. TEM cross-sectional image of (a) the channel region and (b) the contact region of a ZnO nanowire transistor with an aluminum top-gate electrode. In the channel region, the ZnO nanowire has been covered with a SAM prior to the aluminum evaporation. A bright shell is recognized around the circumference of the ZnO nanowire, separating it from the aluminum gate electrode. Further, a dark region is found at the bottom interface of the aluminum gate electrode near the nanowire. In contrast, the aluminum is in intimate contact with the ZnO nanowire in the contact region. (c) Superposition of the bright-field TEM image of the channel cross section and the oxygen elemental map (colored in red) acquired by energy-filtered transmission electron microscopy. The dark region at the bottom interface of the aluminum gate electrode is identified as aluminum oxide (AIO<sub>x</sub>). To quantify the thickness of the bright shell and the aluminum gate electrode is investigated. The profile is obtained by integration of the bright-field image parallel to the top facet of the ZnO nanowire over the indicated integration width (5 nm). The thickness of the aluminum oxide layer and of the bright shell is estimated to 4 nm in this region. Since the thickness of the SAM is expected to be no more than 2.1 nm, the bright shell is thicker than expected, indicating a poor wetting of the aluminum on the SAM-covered ZnO nanowire.

section of another ZnO nanowire cut out from the source/drain contact region of a transistor. In this region, the ZnO nanowire has been exposed to a short argon-plasma treatment prior to the evaporation of the aluminum contact (no SAM). The cross sections of the channel and the contact regions show significant structural differences. In the contact region, the aluminum is in intimate contact with the ZnO nanowire, which allows excellent charge-carrier injection. In contrast, in the channel region, the aluminum gate electrode appears to be separated from the SAM-covered nanowire. A bright shell is recognized around the ZnO nanowire, and a darker region is found at the bottom interface of the aluminum gate electrode near the nanowire. Figure 3c shows a superposition of the bright-field TEM image with the elemental map of oxygen obtained from the energy-filtered transmission electron microscopy (EFTEM) image. For clarity, the elemental map of oxygen has been colored in red. As can be seen, a pronounced oxygen signal is found in the dark regions at the bottom interface of the aluminum gate electrode, which indicates the formation of an aluminum oxide  $(AIO_x)$  layer. It is important to note that no attempts were made to induce the formation of this AlO<sub>x</sub> layer. For both the deposition of the aluminum contacts and the deposition of the aluminum gate electrode, the evaporation chamber was evacuated to a pressure of  $<4 \times 10^{-6}$  mbar (evaporation rate  $\sim 10$  Å/s). The presence of the spontaneously formed AlO<sub>x</sub> layer indicates that atmospheric oxygen can diffuse into the SAM/Al interface. Similar observations have recently been reported for the interface between graphene and vacuum-deposited aluminum.<sup>24</sup>

It is further interesting to note that the distance between the  $AIO_x$  layer and the surface of the ZnO nanowire appears to vary around the circumference of the nanowire. The thickness of the bright shell separating the  $AIO_x$  layer from the ZnO nanowire varies between 2 and 6 nm around the circumference of the ZnO nanowire. As an example, Figure 3c shows the profile obtained by integrating the bright-field TEM image parallel to the top facet of the ZnO nanowires over the indicated integration width (5 nm). The thickness of the  $AIO_x$  layer as well as the thickness of the bright shell are estimated from the TEM profile to be both 4 nm. The interpretation of the bright layer on the basis of the TEM image is difficult. A straightforward assumption is to conclude that the bright shell represents

the SAM. However, the thickness of the SAM should be no more than 2.1 nm (ref 25) and is expected to be constant around the circumference of the nanowire. It is therefore believed that the bright region indicates that the AIO<sub>x</sub> layer is not in intimate contact with the SAM-covered ZnO nanowire. The bright shell might correspond to hollow regions that form at the interface as a consequence of a poor surface wetting of the aluminum on the SAM-covered ZnO nanowire. This hypothesis is supported by Supporting Information Figure S1, which shows TEM cross sections of oxygen- and argon-plasmatreated ZnO nanowires, without SAM, covered with aluminum. In both cases, good wetting of the aluminum on the ZnO surface and intimate AI/ZnO contact are observed, without any indication of a bright shell.

Our hypothesis regarding the formation of hollow regions is further supported by a comparison between the TEM cross sections of aluminum deposited onto a SAM-covered ZnO nanowire and aluminum deposited onto a flat SAM-covered aluminum film (see Figure 4b). The thickness of the bright shell is found to vary only when aluminum is deposited onto the SAM-covered ZnO nanowires but not when aluminum is deposited onto a flat SAM-covered surface, which we believe is due to the larger surface of the ZnO nanowire compared to the flat aluminum film. The formation of hollow regions at the interface to the ZnO nanowire may also facilitate the penetration of atmospheric oxygen and may thereby support the spontaneous formation of the AlO<sub>x</sub> layer. The TEM cross sections of three additional ZnO nanowire channel regions are shown in Figure S2. All of them show a varving thickness of the bright shell around the circumference of the SAM-covered ZnO nanowire.

The TEM analysis therefore provides an explanation for the strongly reduced gate current of ZnO nanowire transistors with an aluminum top-gate electrode, compared to ZnO nanowire transistors with a gold top-gate electrode. The hybrid gate dielectric consisting of the SAM and the spontaneously formed AlO<sub>x</sub> layer provides a much more stable dielectric than the SAM alone.

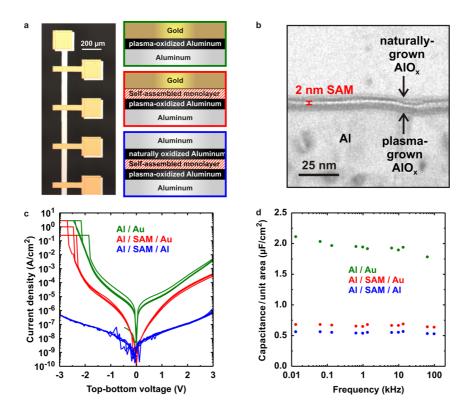

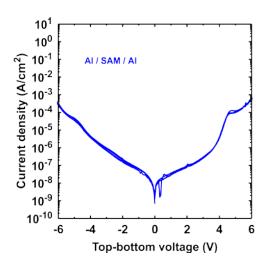

To analyze the influence of the SAM and the spontaneously formed  $AIO_x$  layer on the leakage current density and the capacitance per unit area, large-area leakage current test structures are fabricated with the help of polyimide shadow masks. (The details of the fabrication process can be found in the Supporting Information.) Figure 4a shows a photograph of the test structures and the schematic cross section of the investigated dielectrics (AI/Au, AI/SAM/Au, AI/SAM/Al). For all test structures, the aluminum bottom electrodes are exposed to a soft oxygen-plasma treatment (30 sccm, 10 mTorr, 50 W, 20 s) before the deposition of the top electrode (AI or Au) or before the immersion into the SAM solution (AI/SAM/Au, AI/SAM/Al).

It is important to note that the test structures (Al/SAM/Al) resemble the gate dielectric stack only in the overlap region of the source/drain contacts and the gate electrode of the nanowire FETs. In the channel region of the nanowire FETs, the gate dielectric stack is different due to the poor wetting of the aluminum on the SAM-covered ZnO nanowire. The poor wetting is not observed in the Al/SAM/Al test structure, as can be seen from the TEM cross section in Figure 4b. Nevertheless, the experiment shows the important influence of the spontaneously grown aluminum oxide on the insulating properties of the gate dielectric.

As can be seen from Figure 4c, the spontaneously formed AIO<sub>x</sub> layer has a significant effect on the leakage current density through the test structure. While the addition of the SAM reduces the leakage current density by around 1 order of magnitude (compare green and red curves), the current density is reduced by 2 to 3 orders of magnitude when the gold top electrode is replaced by aluminum (compare red and blue curves). This is especially pronounced for negative voltages where the reduction is even larger than 3 orders of magnitude. (Please note that the leakage current for the junctions with gold top electrode (red curves) is larger compared to the value reported in ref 25. However, this can be attributed to the milder oxygen plasma conditions utilized in the current study.) Simultaneously, the capacitance per unit area (Figure 4d) decreases from 1900 nF/cm<sup>2</sup> (Al/Au) to 680 nF/cm<sup>2</sup> (Al/SAM/Au) to 560 nF/cm<sup>2</sup> (Al/SAM/Al).

Based on the values obtained for the capacitance per unit area of the different dielectrics, the capacitance per unit area of the SAM in combination with the spontaneously oxidized aluminum in the channel region of the nanowire FET can be estimated to be  $\sim$ 790 nF/cm<sup>2</sup>, although this value only gives an upper limit for the true capacitance since the hollow regions identified in the channel region may reduce the actual capacitance in the channel region. Based on this estimation of the gate dielectric capacitance per unit area, the field-effect mobility of the ZnO nanowire FET shown in Figure 2 can be calculated using the following equation:

$$\mu_{\rm sat} = \frac{2L}{\pi r C} \left( \frac{{\rm d} \sqrt{I_{\rm D}}}{{\rm d} V_{\rm GS}} \right)^2$$

where it has been assumed that the channel width of the nanowire FET is one-half of the nanowire circumference. The field-effect mobility of the ZnO nanowire shown in Figure 2 is calculated to be  $50 \text{ cm}^2/\text{Vs}$ , which is almost identical to the mobilities which we measured for ZnO nanowire FETs realized in the global back-gate configuration on Si/SiO<sub>2</sub> substrates based on the same nanowire material.

Please note again that the spontaneous formation of the  $AIO_x$  layer occurs only in the channel region of the transistors (oxygen-plasma treatment and hydrophobic SAM) but not in the contact regions (argon-plasma treatment, no SAM), ensuring efficient charge injection at the contacts.

Figure 4. Leakage current through dielectric test structures. (a) Photograph of leakage current test structures with an aluminum bottom electrode and a gold top electrode. Schematic cross sections of the investigated dielectrics with different composition: Al/Au; Al/SAM/Au; Al/SAM/Al. (b) TEM cross-sectional image of an Al/SAM/Al leakage current test structure. The thickness of the bright shell is only 2 nm and hence coincides with the estimated thickness of the SAM. Further, the thickness of the SAM is constant along the interface. This observation supports the assumption of a poor surface wetting of the aluminum on the SAM-covered ZnO nanowire. (c) Leakage current density as a function of the voltage applied between top and bottom electrode across the different dielectric layers. A dramatic reduction of the leakage current density of around 3 orders of magnitude is observed when the gold top electrode is replaced by aluminum (compare red and blue curves). This is attributed to the spontaneous formation of the additional AlO<sub>x</sub> layer at the interface between aluminum and SAM. (d) Capacitance per unit area of the different dielectrics obtained from leakage current test structures with an overlap area of  $3600 \, \mu m^2$ . To obtain the capacitance, a sine-wave signal with an amplitude of 0.1 V was applied to the top electrode. A lock-in amplifier was used to record the alternating current at the bottom electrode.

Given the small leakage current densities through the hybrid dielectric, we believe that this gate dielectric may also be interesting for the fabrication of thin-film transistors based on ZnO,<sup>26–29</sup> where the overlap areas between gate electrode and semiconductor are much larger compared to transistors based on ZnO nanowires.

The small gate current and the potential to tolerate voltages above 3 V make it possible to operate ZnO nanowire transistors with aluminum top-gate electrodes with much larger overdrive voltages compared to the previously investigated gold top-gate ZnO nanowire transistors and to integrate them with organic LEDs. Figure 5a,b shows the transfer and output characteristics of a transistor with a channel length of 1  $\mu$ m. In order to obtain a large drain current and a large transconductance, the source and drain contacts have been designed in a comb-like pattern, with a total of nine contact fingers (see inset in Figure 5a for a microscopy image and Figure 5c for a schematic). The transistor has an on/off current ratio of 10<sup>8</sup>, a subthreshold slope of 100 mV/dec, and a peak transconductance of 50  $\mu$ S. From the output characteristics, a slightly

n the output characteris

nonlinear increase of the drain current with increasing  $V_{\rm DS}$  can be observed for small  $V_{\rm DS}$  at large  $V_{\rm GS}$ . This can be attributed to the small width of the contact fingers of only 500 nm, which might introduce a non-negligible contact resistance at large overdrive voltages.<sup>30</sup> The maximum drain current at  $V_{GS} = 3 V$  and  $V_{DS} = 3 V$  is 125  $\mu$ A. The large drain current can be used to drive an organic LED to a sufficiently high brightness for practical display applications. The transistor is connected to an organic LED, as depicted in Figure 5c. The organic LED is a green phosphorescent device manufactured by Novaled (Dresden, Germany). It has a luminous efficiency of 31 cd/A and an active area of 6.7 mm<sup>2</sup>. Figure 5d shows four photographs of the green organic LED driven by the ZnO nanowire transistor at a drain potential of  $V_2 = 5.5$  V and gate potentials of  $V_1 = 0, 3.5$ , 4.5, and 5.5 V. As expected, the FET is capable of modulating the brightness of the LED with increasing gate potential. For a gate potential of 0 V, the current driven through the LED is smaller than 1 pA. This is a particularly critical requirement for FETs intended for active-matrix display backplanes since these FETs must

VOL.8 • NO.7 • 6840-6848 • 2014

agnanc www.acsnano.org

Figure 5. Organic LED driven by a ZnO nanowire transistor. (a) Transfer and (b) output characteristics of a ZnO nanowire transistor with aluminum top-gate electrode with source and drain contacts realized in a comb-like pattern. For a drain-source voltage of 2 V, the transistor has a peak transconductance of 50  $\mu$ S, an on/off ratio of 10<sup>8</sup>, and a subthreshold slope of 100 mV/dec The inset shows a photograph of the transistor. (c) Schematic of the comb-like pattern, photograph of the green organic LED, and circuit schematic. (d) Photographs of the light-emitting area (6.7 mm<sup>2</sup>) of the green organic LED for different gate potentials  $V_1$ . For  $V_1 = 5.5$  V, a current of 96  $\mu$ A flows through the organic LED which is sufficient to drive the organic LED to a brightness of 445 cd/m<sup>2</sup>.

provide not only large on-state currents but also extremely small off-state currents, which further underlines the importance of a small doping concentration. For a gate potential of 5.5 V, a current of 96  $\mu$ A is driven through the LED, producing a brightness of 445 cd/m<sup>2</sup>. This demonstrates the general feasibility of the presented approach based on a hybrid top-gate dielectric for the application in AMOLED displays. However, in order to design the comblike pattern for the source and drain contacts of the ZnO nanowire FET demonstrated in Figure 5a, the use of electron-beam lithography is essential. Certainly, electronbeam lithography is not a suitable patterning technique for flat-panel displays, but taking into account that a typical display subpixel area is only around  $10^{-4}$  cm<sup>2</sup>, and hence around 2 orders of magnitude smaller compared to the organic LED used in this demonstration, the transistor geometry in an actual pixel could be much more relaxed. We therefore expect that the patterning with electron-beam lithography could eventually be readily replaced by photolithography (as shown, for example, in ref 9) while maintaining the performance necessary to drive organic LEDs to sufficient brightness.

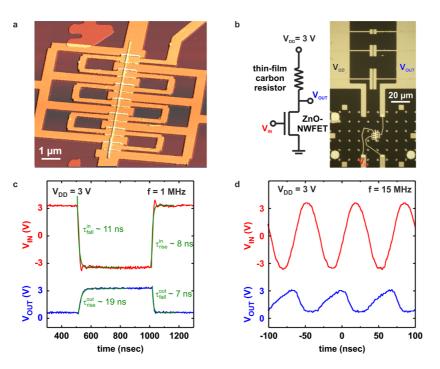

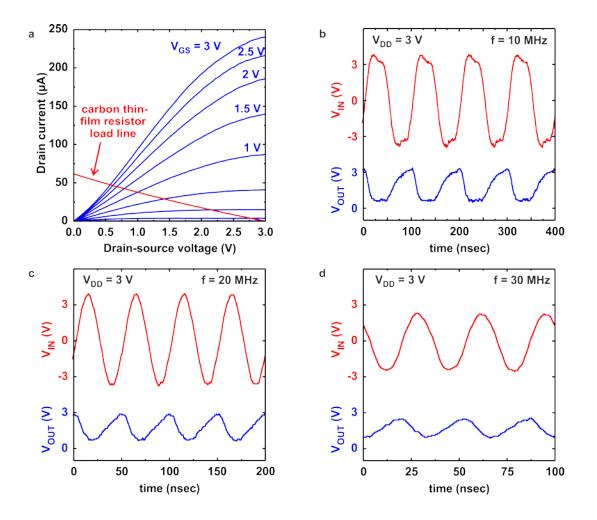

To estimate the dynamic performance of the aluminum top-gate ZnO nanowire transistors, inverters based on a ZnO nanowire transistor and a load resistor based on a patterned thin film of carbon are fabricated on insulating glass substrates. The fabrication of the thin-film carbon resistors is detailed in ref 31. Again, a comb-like pattern has been chosen for the source and drain contacts of the ZnO nanowire FETs in order obtain a large transconductance. An AFM image of the transistor based on a 60 nm thick ZnO nanowire is depicted in Figure 6a. The transistor has a channel length of 0.5  $\mu$ m and a total of eight contact fingers. Figure 6b shows the circuit schematic and a microscopy image of the inverter with a thin-film carbon load resistor that has a total width of 35  $\mu$ m and a length of 1  $\mu$ m.

The resistance of the thin-film carbon resistor is 50 k $\Omega$ . The load curve of the resistor together with the output curves of the transistor is shown in Figure S4a. The dynamic response of the inverter is characterized using an active probe needle (GGB Industries Picoprobe 19C) with a total capacitance of  $C_{\rm pico} \sim 150$  fF. Figure 6c shows the dynamic response of the inverter to a square-wave input signal with a frequency of 1 MHz at supply voltage of 3 V. The extracted time constants are obtained from exponential fits to the input and output signals (see Supporting Information). Due to the large transconductance of the transistor (50  $\mu$ S), charging the output node from high potential to low potential happens almost instantaneously, as confirmed by the extracted time constants:  $\tau_{rise}^{in} = 8$  ns and  $\tau_{\text{fall}}^{\text{out}} = 7$  ns. In contrast, charging the output node from low to high potential through the 50 k $\Omega$  load resistor occurs with a delay; that is, the time constant of the output signal  $\tau_{\rm rise}^{\rm out}$  = 19 ns is larger than the time

VOL. 8 • NO. 7 • 6840-6848 • 2014

JAI

www.acsnano.org

Figure 6. Inverter with thin-film carbon resistor and dynamic characterization. (a) Tilted atomic force microscopy image of a ZnO nanowire transistor with a comb-like pattern for the source and drain contacts. The transistor has a channel length of 0.5  $\mu$ m, and the thickness of the ZnO nanowire is 60 nm. (b) Circuit schematic and photograph of an inverter based on a ZnO nanowire transistor and a thin-film carbon load resistor on a glass substrate. AuPd electrodes were patterned on the thin-film carbon by electron-beam lithography. The resistor has a width of 35  $\mu$ m and a length of 1  $\mu$ m, providing a resistance of 50 kΩ. (c) Exponential fits (green) to the square-wave input signal (red) and to the dynamic response of the inverter (blue) at a frequency of 1 MHz. As can be seen from the extracted time constants, charging the output node from low potential to high potential through the 50 kΩ load resistor introduces a delay, while charging the output node from high to low potential through the stantaneously. (d) Dynamic response of the inverter with a frequency of 15 MHz to a sine-wave input signal at a supply voltage of 3 V.

constant of the input signal  $\tau_{fall}^{in} = 11$  ns. Figure 6d shows the dynamic response of the inverter to a sine-wave input signal with a frequency of 15 MHz at a supply voltage of 3 V. For a transconductance of  $g_m = 50 \,\mu$ S, this frequency is close to the calculated cutoff frequency

$$f_{\rm T} = g_{\rm m}/(2\pi C_{\rm pico})$$

of 50 MHz. (Figure S4b–d illustrates the dynamic response for frequencies up to 30 MHz.) It should be noted that the switching frequency is limited by the capacitance of the active probe needle (150 fF). Based on the estimated gate capacitance per unit area, the total device capacitance is expected to be around 10 fF, so a cutoff frequency near 750 MHz is projected for this transistor.

#### CONCLUSION

In conclusion, we have demonstrated high-performance top-gate field-effect transistors based on ZnO nanowires and a hybrid organic/inorganic gate dielectric consisting of a self-assembled monolayer and aluminum oxide. The hybrid dielectric forms naturally when aluminum is thermally evaporated onto a SAMcovered ZnO nanowire since atmospheric oxygen can penetrate the interface between the SAM and aluminum. Cross-sectional TEM images indicate that the aluminum gate electrode is only poorly wetting the SAM-covered ZnO nanowire which is beneficial for the penetration of atmospheric oxygen. The transistors have an on/off current ratio of 10<sup>8</sup>, a subthreshold swing of 100 mV/dec, and a transconductance of 50  $\mu$ S. The hybrid gate dielectric allows operating the transistors at voltages up to 3 V, making them fully compatible with organic LEDs. Inverters based on ZnO nanowire transistors with hybrid gate dielectric operate at frequencies up to 30 MHz. As the maximum temperature during the fabrication of the hybrid gate dielectric is 100 °C, the developed process is compatible with flexible polymeric substrates.

#### **METHODS**

The hydrothermally synthesized ZnO nanowires were randomly dispersed onto a glass substrate or onto a heavily doped silicon substrate covered with 100 nm thick thermally grown SiO<sub>2</sub> and located by microscopy with respect to a marker array.

th respect to a marker array. 100 V

100 W, 15 s) to clean the nanowire surface and increase the ZnO VOL. 8 • NO. 7 • 6840–6848 • 2014

The source and drain contacts were patterned by electronbeam lithography, vacuum evaporation of 80 nm thick alumi-

num, and lift-off. Immediately prior to the evaporation of the

aluminum contacts, the contact regions of the nanowires

were briefly exposed to an argon plasma (30 sccm Ar, 10 mTorr,

www.acsnano.org

surface conductivity by preferential sputtering of oxygen. Next, the regions for the gate electrodes were defined by EBL, followed by exposing the substrate to a soft oxygen plasma (30 sccm  $O_2$ , 10 mTorr, 50 W, 20 s) to increase the density of hydroxyl groups on the surface of the ZnO nanowire channel and on the surface of the aluminum source and drain contacts in the area of the gate electrode. The sample was then immersed into a solution of octadecylphosphonic acid in 2-propanol to form a self-assembled monolayer on the ZnO nanowire and on the aluminum contacts. After 1 h, the substrate was removed from the solution, rinsed with 2-propanol, and baked on a hot plate at 100 °C for 10 min to evaporate excess solvent and improve the quality of the monolayer. Finally, 80 nm thick aluminum was deposited by thermal evaporation to form the metal gate electrode, followed by the lift-off of excess metal.

*Conflict of Interest:* The authors declare no competing financial interest.

Acknowledgment. This work was funded by the German Research Foundation (DFG) under Grant KL 2223/3-1 (Materials World Network).

Supporting Information Available: TEM cross sections of the ZnO/AI, ZnO/SAM/AI, and AI/SAM/AI interfaces and additional information on the fabrication of the leakage current test structures, on the breakdown voltage tests, and on the dynamic performance of ZnO-nanowire-based inverters. This material is available free of charge *via* the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- McAlpine, M. C.; Friedman, R. S.; Jin, S.; Lin, K. H.; Wang, W. U.; Lieber, C. M. High-Performance Nanowire Electronics and Photonics on Glass and Plastic Substrates. *Nano Lett.* 2003, *3*, 1531–1535.

- Zhang, W. F.; He, Z. B.; Yuan, G. D.; Jie, J. S.; Luo, L. B.; Zhang, X. J.; Chen, Z. H.; Lee, C. S.; Zhang, W. J.; Lee, S. T. High-Performance, Fully Transparent, and Flexible Zinc-Doped Indium Oxide Nanowire Transistors. *Appl. Phys. Lett.* **2009**, *94*, 123103.

- Kwon, S. S.; Hong, W. K.; Jo, G.; Maeng, J.; Kim, T. W.; Song, S.; Lee, T. Piezoelectric Effect on the Electronic Transport Characteristics of ZnO Nanowire Field-Effect Transistors on Bent Flexible Substrates. *Adv. Mater.* 2008, 20, 4557–4562.

- Kang, J.; Keem, K.; Jeong, D. Y.; Kim, S. Electrical Characteristics of ZnO Nanowire-Based Field-Effect Transistors on Flexible Plastic Substrates. Jpn. J. Appl. Phys. 2007, 46, 6227–6229.

- McAlpine, M. C.; Ahmad, H.; Wang, D.; Heath, J. R. Highly Ordered Nanowire Arrays on Plastic Substrates for Ultrasensitive Flexible Chemical Sensors. *Nat. Mater.* 2007, *6*, 379–384.

- Duan, X.; Niu, C.; Sahi, V.; Chen, J.; Wallace Parce, J.; Empedocles, S.; Goldman, J. L. High-Performance Thin-Film Transistors Using Semiconductor Nanowires and Nanoribbons. *Nature* 2003, 425, 274–278.

- Fan, Z.; Ho, J. C.; Jacobson, Z. A.; Yerushalmi, R.; Alley, R. L.; Razavi, H.; Javey, A. Wafer-Scale Assembly of Highly Ordered Semiconductor Nanowire Arrays by Contact Printing. *Nano Lett.* **2008**, *8*, 20–25.

- Liu, X. M.; Long, Y. Z.; Liao, L.; Duan, X.; Fan, Z. Large-Scale Integration of Semiconductor Nanowires for High-Performance Flexible Electronics. ACS Nano 2012, 6, 1888–1900.

- Ju, S.; Li, J.; Liu, J.; Chen, P.; Ha, Y.; Ishikawa, F.; Chang, H.; Zhou, C.; Facchetti, A.; Janes, D.; *et al.* Transparent Active Matrix Organic Light-Emitting Diode Displays Driven by Nanowire Transistor Circuitry. *Nano Lett.* **2008**, *8*, 997– 1004.

- Zhang, W.; Jie, J.; He, Z.; Tao, S.; Fan, X.; Zhou, Y.; Yuan, G.; Luo, L.; Zhang, W.; Lee, C. S.; *et al.* Single Zinc-Doped Indium Oxide Nanowire as Driving Transistor for Organic Light-Emitting Diode. *Appl. Phys. Lett.* **2008**, *92*, 153312.

- Chen, P. C.; Shen, G.; Chen, H.; Ha, Y. G.; Wu, C.; Sukcharoenchoke, S.; Fu, Y.; Liu, J.; Facchetti, A.; Marks, T. J.; *et al.* High-Performance Single-Crystalline Arsenic-Doped Indium Oxide Nanowires for Transparent Thin-Film

- Keem, K.; Jeong, D.; Kim, S.; Lee, M.; Yeo, I.; Chung, U.; Moon, J. Fabrication and Device Characterization of Omega-Shaped-Gate ZnO Nanowire Field-Effect Transistors. *Nano Lett.* **2006**, *6*, 1454–1458.

- Wu, P.; Ye, Y.; Sun, T.; Peng, R.; Wen, X.; Xu, W.; Liu, C.; Dai, L. Ultrahigh-Performance Inverters Based on CdS Nanobelts. ACS Nano 2009, 3, 3138–3142.

- Kessels, W. M. M.; Putkonen, M. Advanced Process Technologies: Plasma, Direct-Write, Atmospheric Pressure, and Roll-to-Roll ALD. *MRS Bull.* **2011**, *36*, 907–913.

- Lee, Y. T.; Kim, J. K.; Ha, R.; Choi, H. J.; Im, S. ZnO Nanowire Transistor Inverter Using Top-Gate Electrodes with Different Work Functions. *Appl. Phys. Lett.* **2011**, *99*, 153507.

- Lee, Y. T.; Raza, S. R. A.; Jeon, P. J.; Ha, R.; Choi, H.-J.; Im, S. Long Single ZnO Nanowire for Logic and Memory Circuits: NOT, NAND, NOR Gate, and SRAM. *Nanoscale* **2013**, *5*, 4181–4185.

- Kälblein, D.; Weitz, R. T.; Böttcher, H. J.; Ante, F.; Zschieschang, U.; Kern, K.; Klauk, H. Top-Gate ZnO Nanowire Transistors and Integrated Circuits with Ultrathin Self-Assembled Monolayer Gate Dielectric. *Nano Lett.* 2011, *11*, 5309–5315.

- Lu, C.; Qi, L.; Yang, J.; Tang, L.; Zhang, D.; Ma, J. Hydrothermal Growth of Large-Scale Micropatterned Arrays of Ultralong ZnO Nanowires and Nanobelts on Zinc Substrate. *Chem. Commun.* **2006**, 3551–3553.

- Lee, J. M.; Kim, K. K.; Park, S. J.; Choi, W. K. Low-Resistance and Nonalloyed Ohmic Contacts to Plasma Treated ZnO. *Appl. Phys. Lett.* **2001**, *78*, 3842–3844.

- Ra, H. W.; Choi, K. S.; Ok, C. W.; Jo, S. Y.; Bai, K. H.; Im, Y. H. Ion Bombardment Effects on ZnO Nanowires during Plasma Treatment. *Appl. Phys. Lett.* **2008**, *93*, 033112.

- Walzer, K.; Maennig, B.; Pfeiffer, M.; Leo, K. Highly Efficient Organic Devices Based on Electrically Doped Transport Layers. *Chem. Rev.* 2007, *107*, 1233–1271.

- 22. Brillson, L. J.; Lu, Y. ZnO Schottky Barriers and Ohmic Contacts. J. Appl. Phys. 2011, 109, 121301.

- Özgür, U.; Alivov, Y. I.; Liu, C.; Teke, A.; Reshchikov, M. A.; Doğan, S.; Avrutin, V.; Cho, S. J.; Morkoçd, H. A Comprehensive Review of ZnO Materials and Devices. *J. Appl. Phys.* 2005, *98*, 041301.

- Li, S. L.; Miyazaki, H.; Kumatani, A.; Kanda, A.; Tsukagoshi, K. Low Operating Bias and Matched Input–Output Characteristics in Graphene Logic Inverters. *Nano Lett.* **2010**, *10*, 2586–2600.

- Klauk, H.; Zschieschang, U.; Pflaum, J.; Halik, M. Ultralow-Power Organic Complementary Circuits. *Nature* 2007, 445, 745–748.

- Bayraktaroglu, B.; Leedy, K.; Neidhard, R. Microwave ZnO Thin-Film Transistors. *IEEE Electron Device Lett.* 2008, 29, 1024–1026.

- Mourey, D. A.; Zhao, D. A.; Sun, J.; Jackson, T. N. Fast PEALD ZnO Thin-Film Transistor Circuits. *IEEE Trans. Electron Devices* 2010, *57*, 530–534.

- Adamopoulos, G.; Bashir, A.; Thomas, S.; Gillin, W. P.; Georgakopoulos, S.; Shkunov, M.; Baklar, M. A.; Stingelin, N.; Maher, R. C.; Cohen, L. F.; *et al.* Spray-Deposited Li-Doped ZnO Transistors with Electron Mobility Exceeding 50 cm<sup>2</sup>/Vs. *Adv. Mater.* **2010**, *22*, 4764–4769.

- Faber, H.; Burkhardt, M.; Jedaa, A.; Kälblein, D.; Klauk, H.; Halik, M. Low-Temperature Solution-Processed Memory Transistors Based on Zinc Oxide Nanoparticles. *Adv. Mater.* 2009, *21*, 3099–3104.

- Ante, F.; Kälblein, D.; Zaki, T.; Zschieschang, U.; Takimiya, K.; Ikeda, M.; Sekitani, T.; Someya, T.; Burghartz, J. N.; Kern, K.; *et al.* Contact Resistance and Megahertz Operation of Aggressively Scaled Organic Transistors. *Small* **2012**, *8*, 73–79.

- Ryu, H.; Kälblein, D.; Schmidt, O. G.; Klauk, H. Unipolar Sequential Circuits Based on Individual-Carbon-Nanotube Transistors and Thin-Film Carbon Resistors. ACS Nano 2011, 5, 7525–7531.

## Supporting Information

## **High-Performance ZnO-Nanowire Transistors with Aluminum Top-Gate Electrodes and Naturally Formed** Hybrid Self-Assembled Monolayer/AlO<sub>x</sub> Gate Dielectric

Daniel Kälblein,<sup>1</sup> Hyeyeon Ryu,<sup>1</sup> Frederik Ante,<sup>1</sup> Bernhard Fenk,<sup>1</sup> Kersten Hahn,<sup>2</sup> Klaus Kern,<sup>1,3</sup> and Hagen Klauk<sup>1</sup>

- <sup>1</sup> Max Planck Institute for Solid State Research, 70569 Stuttgart, Germany

<sup>2</sup> Max Planck Institute for Intelligent Systems, 70569, Stuttgart, Germany

## **Table of Contents**

- 1. TEM cross-sections of the ZnO/Al interface (without SAM)

- 2. TEM cross-sections of ZnO/SAM/Al and Al/SAM/Al interfaces

- 3. Leakage current test structures and breakdown voltage test

- 4. Dynamic performance of ZnO-nanowire-based inverters

<sup>&</sup>lt;sup>3</sup> Institut de Physique de la Matière Condensée, École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland

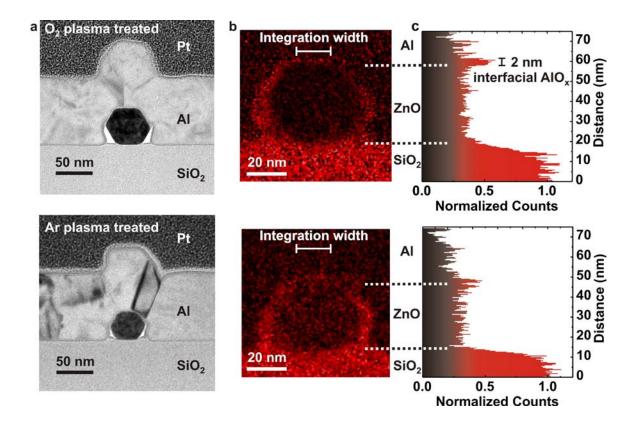

## 1. TEM cross-sections of the ZnO/Al interface (without SAM)

Figure S1. TEM cross-sections of the ZnO/Al interface (without SAM)

The images in the <u>upper row</u> correspond to a ZnO nanowire that was exposed to an <u>oxygen plasma</u> prior to the aluminum deposition; the images in the <u>lower row</u> correspond to a ZnO nanowire exposed to an <u>argon plasma</u> prior to the aluminum deposition. In both cases, the SAM treatment was omitted, so there is <u>no SAM</u> covering the surface of the ZnO nanowires. In both cases, the substrate is a thermally oxidized Si wafer and the deposited aluminum layer has a thickness of 80 nm.

- a) Bright-field TEM cross-sectional images.

- b) Elemental map of oxygen obtained from the TEM cross-sections.

- c) Oxygen profiles obtained by integrating the elemental maps of oxygen parallel to the top facet of the nanowires over the indicated integration width (16 nm).

Both oxygen profiles show an increased oxygen signal at the ZnO/Al interface. However, in the case of the oxygen-plasma-treated nanowire (upper row), the oxygen signal is more pronounced than in the case of the argon-plasma-treated nanowire (lower row), indicating the formation of an interfacial  $AlO_x$  layer with a thickness of approximately 2 nm.

## 2. TEM cross-sections of ZnO/SAM/Al and Al/SAM/Al interfaces

# Figure S2. TEM cross-sections of the interface between aluminum deposited by thermal evaporation onto SAM-covered ZnO nanowires and onto a flat, plasma-oxidized and SAM-covered aluminum surface

- a), b), c) Bright-field TEM cross-sectional images of three different ZnO nanowires treated with an oxygen plasma and covered with an octadecylphosphonic acid SAM prior to the Al deposition. As can be seen, the thickness and extension of the bright shell that separates the SAM-covered ZnO nanowire from the spontaneously formed  $AlO_x$  layer varies around the nanowire circumference and also from nanowire to nanowire. While the thickness of the SAM is expected to be no more than 2.1 nm, the bright shell is as thick as 8 nm.

- d) Bright-field TEM cross-sectional images of a flat Al/SAM/Al sandwich structure. The thickness of the bright shell is only 2 nm, coinciding with the estimated thickness of the SAM. Further, the thickness of the SAM is constant along the interface. This observation supports the hypothesis of a poor surface wetting of the aluminum on the SAM-covered ZnO nanowires, leading to the formation of a hollow region around the nanowire circumference.

### 3. Leakage current test structures and breakdown voltage test

To investigate the leakage current density through the hybrid AlO<sub>x</sub>/SAM dielectric, largearea leakage current test structures are fabricated. First, the bottom electrodes are patterned by thermal evaporation of aluminum (80 nm) through a polyimide shadow mask (CADiLAC Laser, Hilpoltstein, Germany). Next, gold (30 nm) is evaporated through another shadow mask to define vias in the regions of the contact pads, which helps to avoid the formation of an AlO<sub>x</sub> layer and a SAM on the aluminum in these regions. Next, the samples are exposed to an oxygen plasma (30 sccm O<sub>2</sub>, 10 mTorr, 50 W, 20 sec). The samples are then immersed into a solution of 2-propanol and octadecylphosphonic acid molecules for the formation of a SAM. After 1 h the samples are removed from the solution, rinsed with 2-propanol and briefly baked on a hotplate (100 °C). Finally, the top electrodes (gold or aluminum, 80 nm thick) are patterned by another shadow-mask evaporation. Figure S3 shows the measured current density for applied voltages up to 6 V. The hybrid AlO<sub>x</sub>/SAM dielectric can sustain voltages of 6 V without any indication of junction breakdown. For positive voltages exceeding 4.5 V, the evolution of bubbles in the junction area is observed; however, from the measured leakage current density, these bubbles do not result in dielectric breakdown.

Figure S3. Breakdown voltage test of hybrid dielectric

Breakdown voltage test of the Al/SAM/Al dielectric. For negative voltages, no junction damage is observed for voltages up to -6 V.

## 4. Dynamic performance of ZnO-nanowire-based inverters

The following functions were utilized for the exponential fits in Figure 6c:

$$\tau_{fall}: V = V_0 + A e^{-\frac{t - t_0}{\tau_{fall}}} \qquad \tau_{rise}: V = V_0 + A \left(1 - e^{-\frac{t - t_0}{\tau_{rise}}}\right)$$

where  $V_{0 is}$  the voltage offset, A is the voltage amplitude,  $t_0$  is the time offset, and  $\tau$  is the characteristic time constant.

Figure S4. Dynamic response of an inverter based on a ZnO-nanowire transistor and a thin-film carbon load resistor.

- a) Output characteristics of the ZnO-nanowire transistor (blue lines) shown in Figure 6a and load curve of the thin-film carbon resistor (red line).

- b), c), d) Dynamic response of the inverter to a square-wave input signal with a frequency of 10 MHz (b), to a sine-wave input signal with a frequency of 20 MHz (c), and to a sine-wave input signal with a frequency of 30 MHz (d).